Ch01 Introduction

Yang Haoran 10/31/2022 FPGAVHDL

# Introduction

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity led is

Port(

switch_1 : in std_logic;

switch_2 : in std_logic;

led_1: out std_logic;

led_2: out std_logic

);

-- Port ( );

end led;

architecture Behavioral of led is

begin

led_1 <= switch_1;

led_2 <= switch_2;

end Behavioral;

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

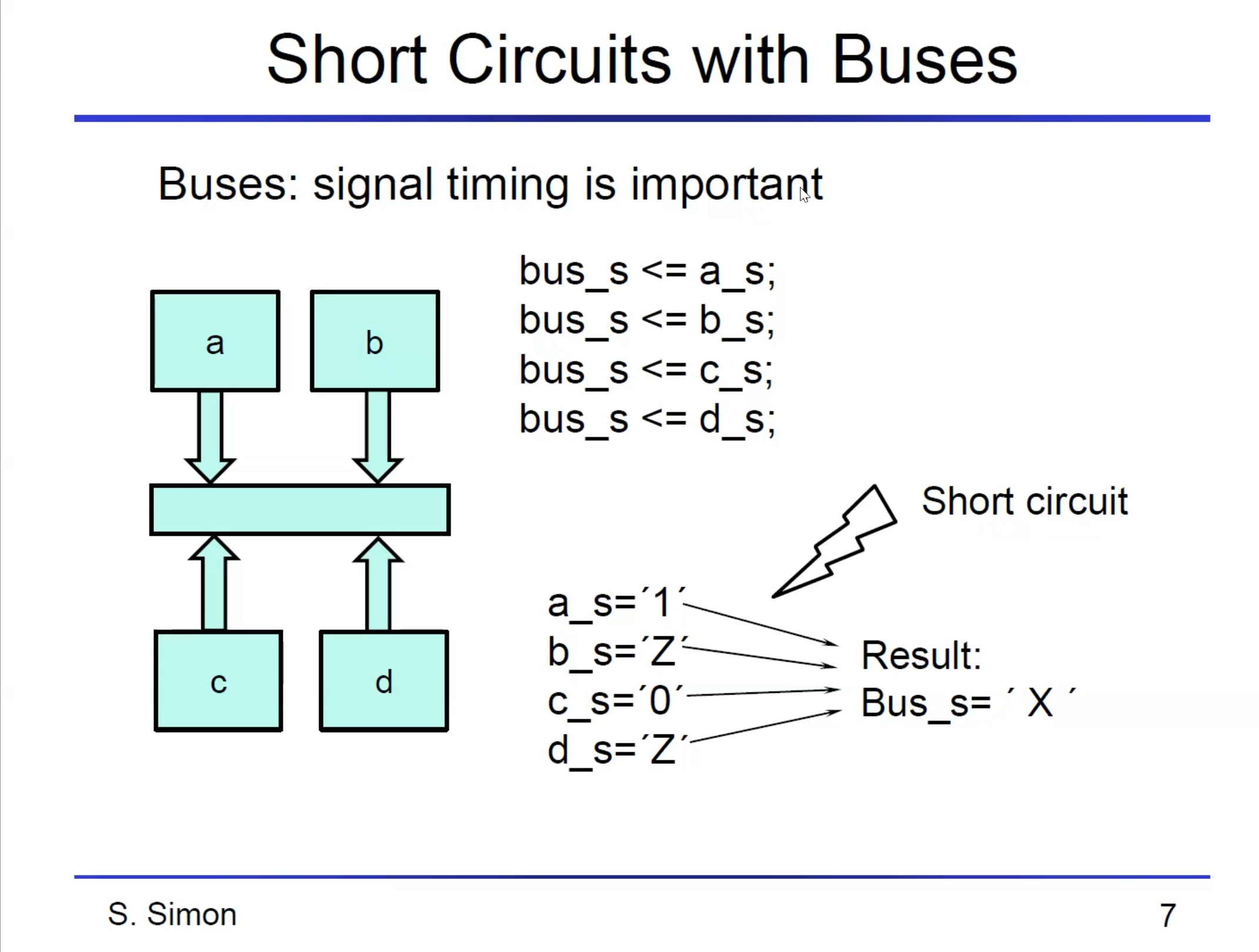

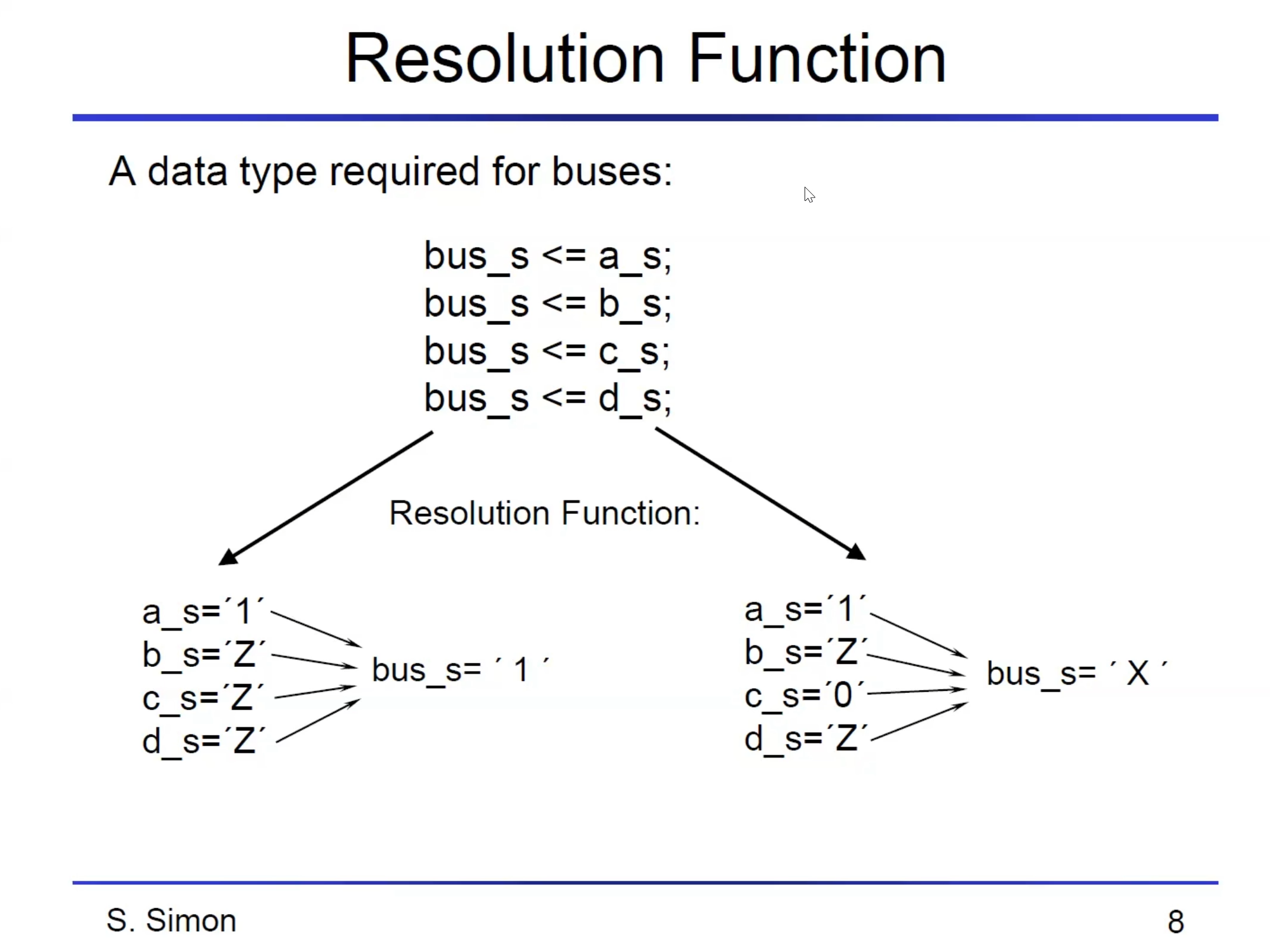

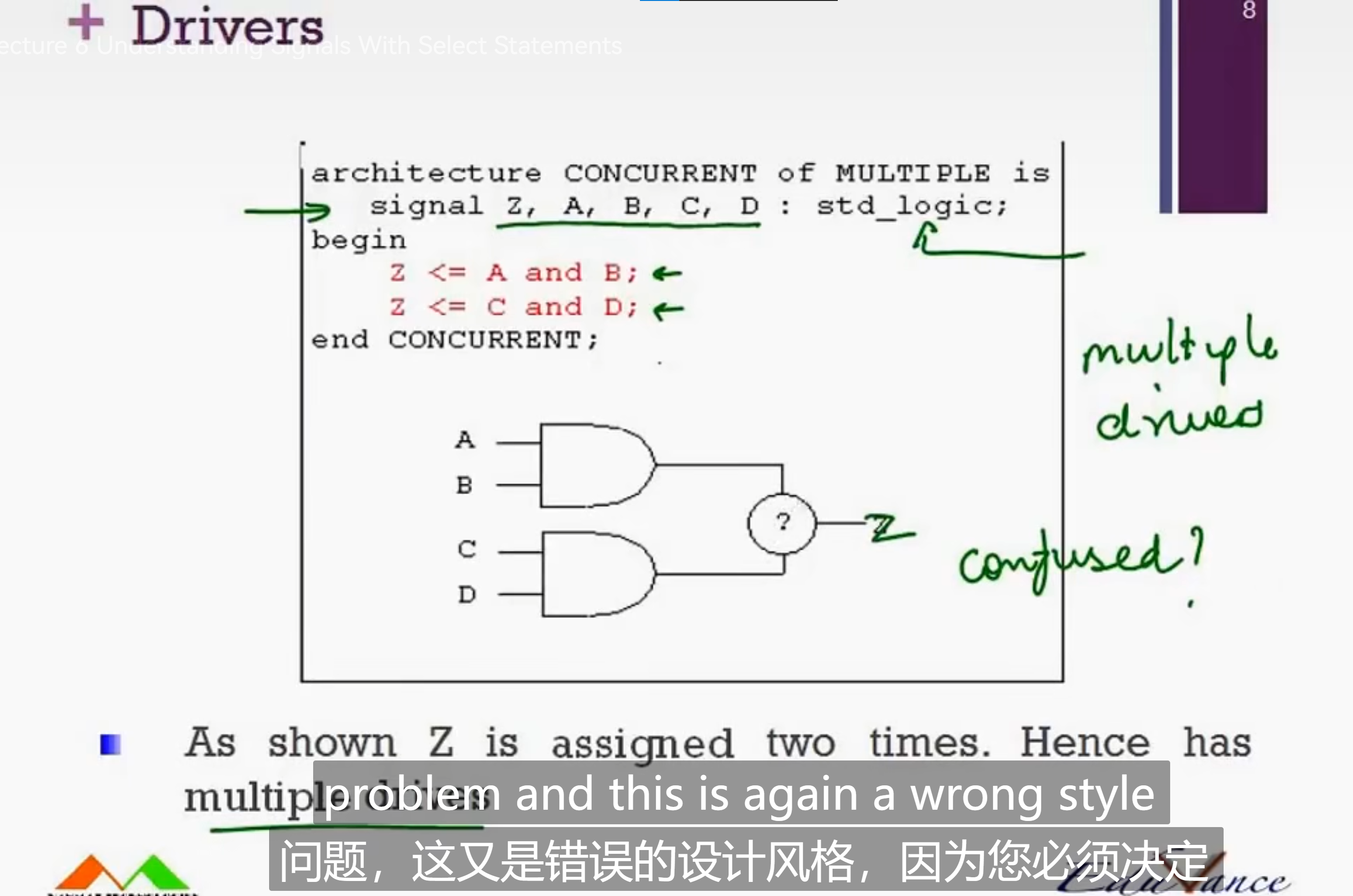

architecture中的语句都是并行(同时)执行,不是顺序执行

- 横坐标和纵坐标同时assign,看最后的结果是什么

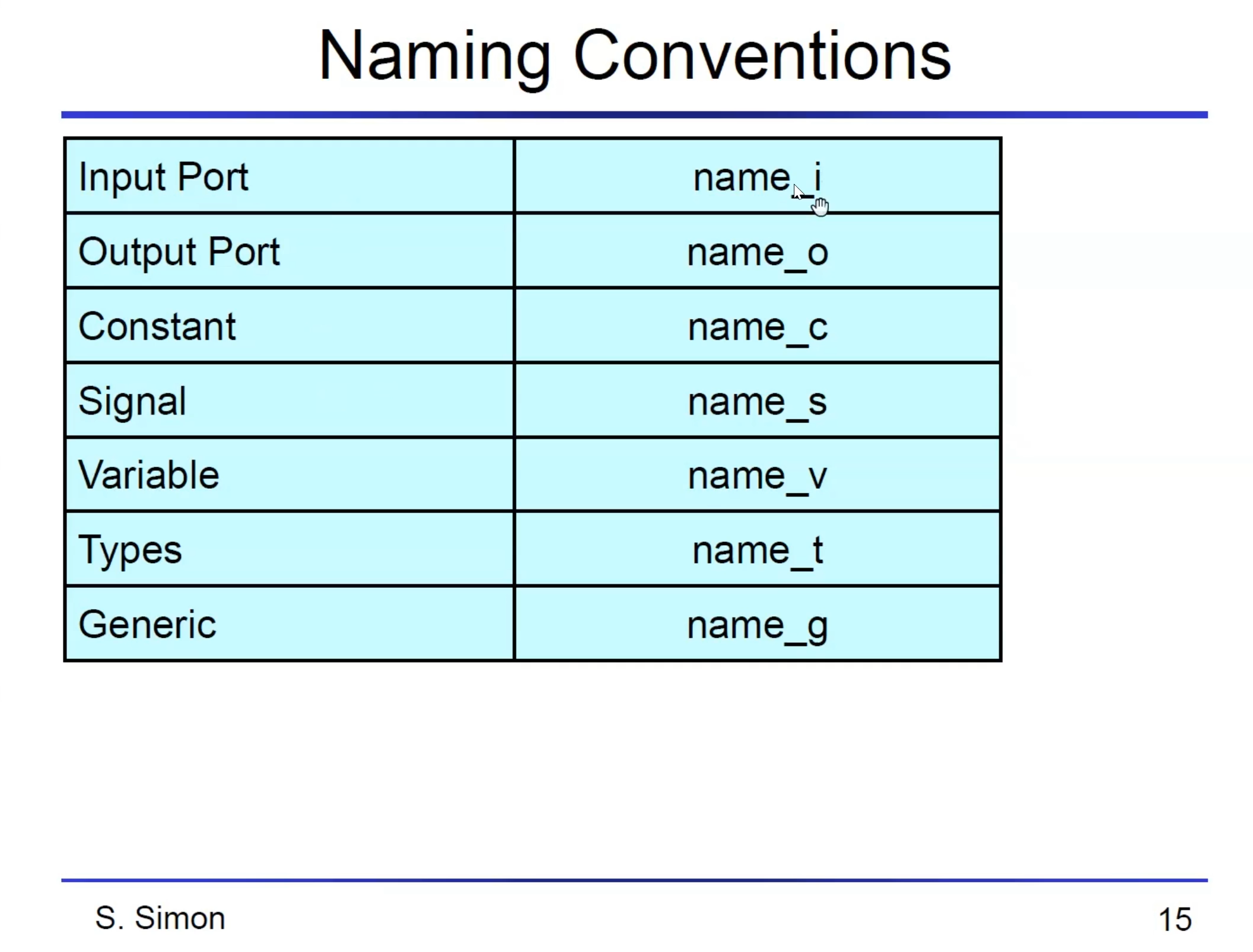

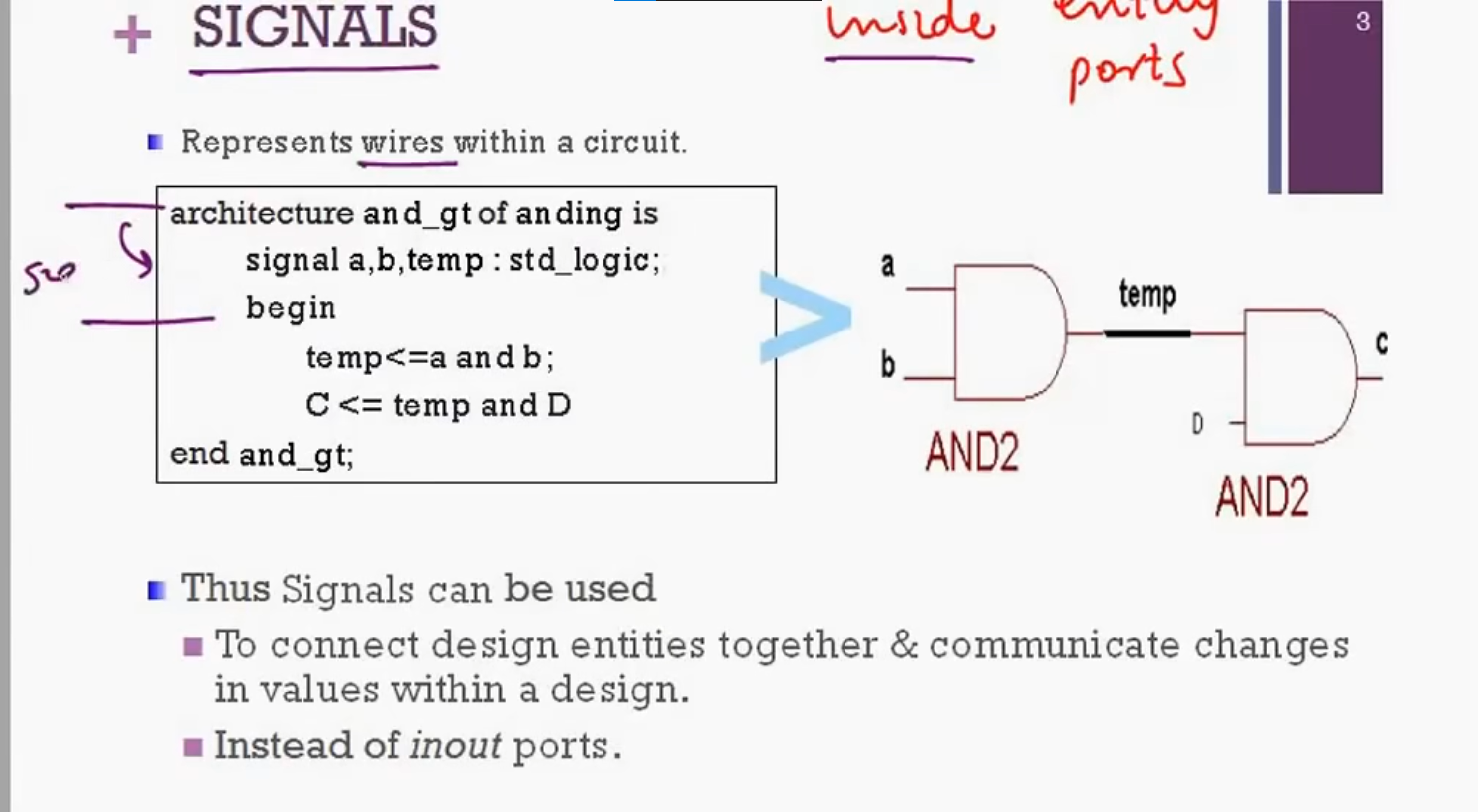

# signal

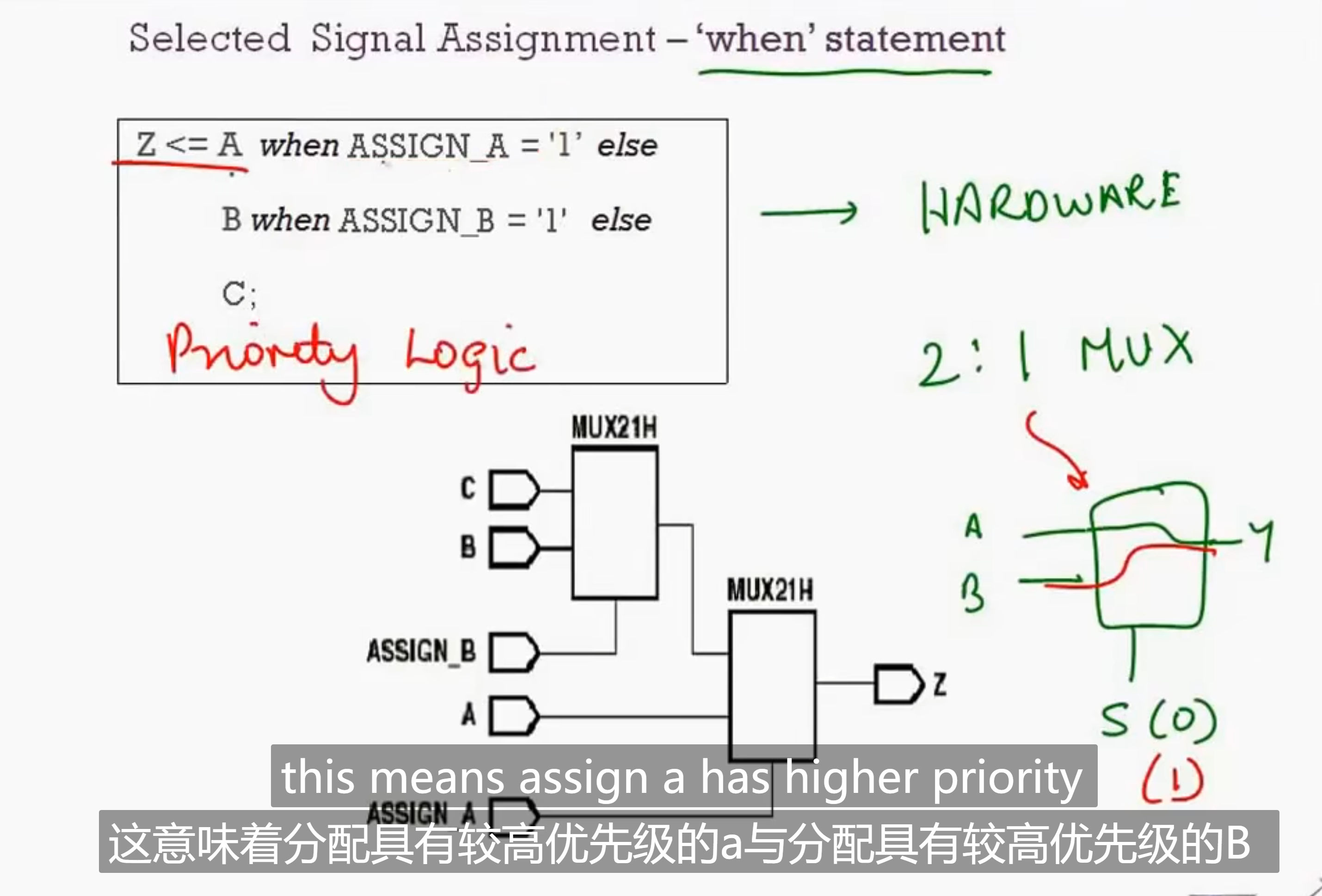

# When

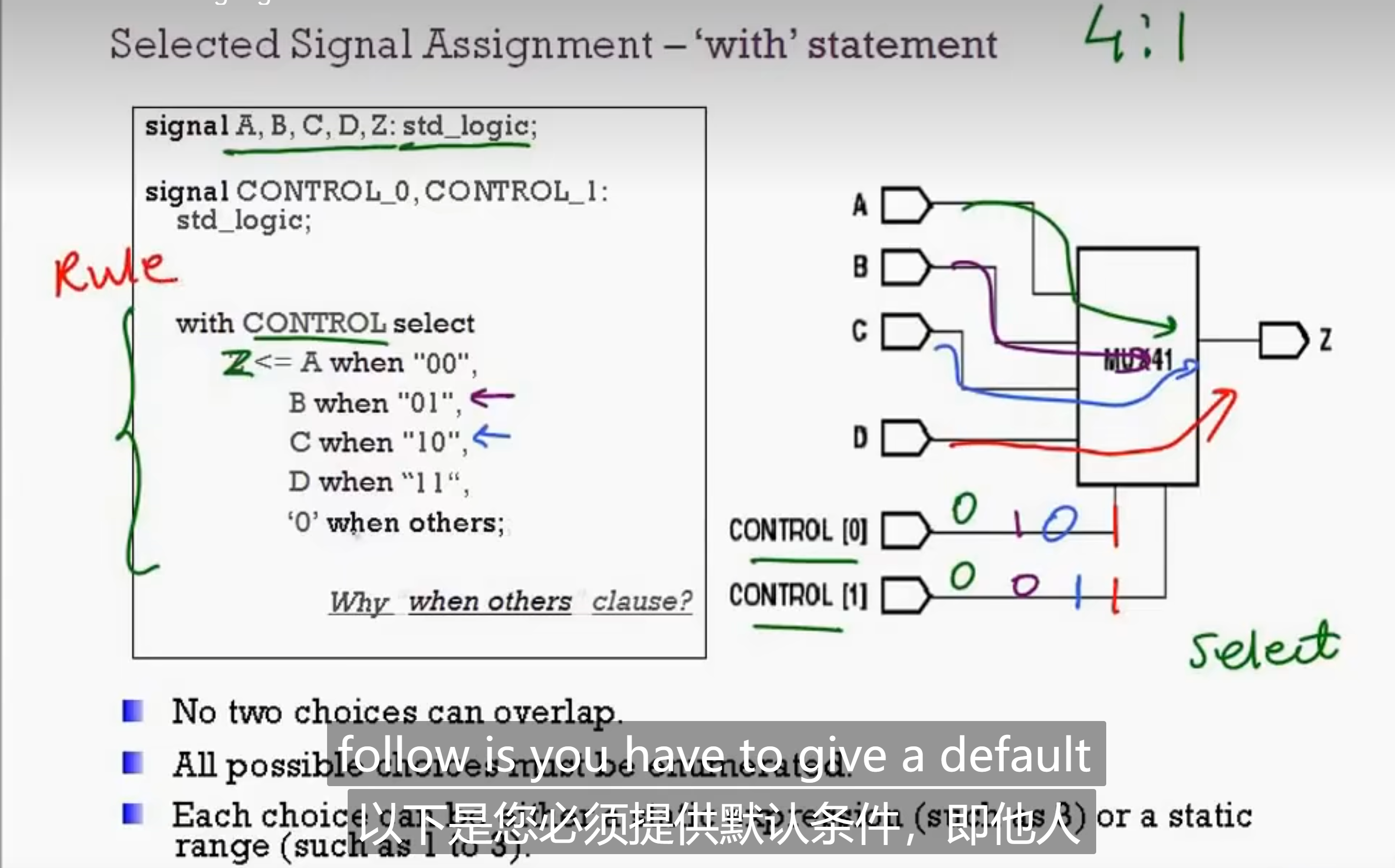

# With select