Ch05 Adder

Yang Haoran 11/24/2022 FPGAVHDL

#

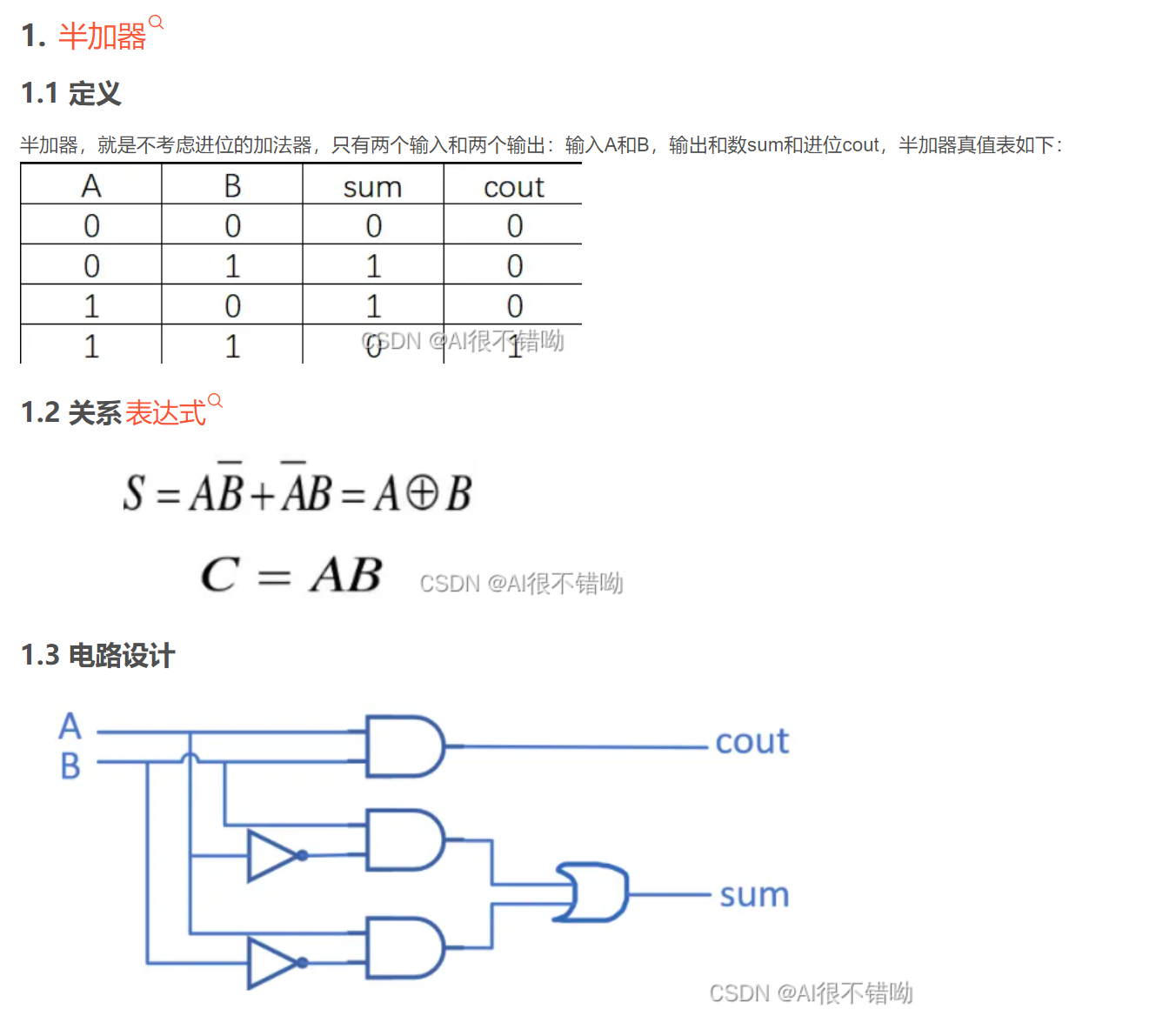

h_adder.vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity h_adder is

port (

in0_i, in1_i : in std_logic;

s_o, cry_o : out std_logic

);

end h_adder;

architecture rtl of h_adder is

begin

s_o <= in0_i xor in1_i;

cry_o <= in0_i and in1_i;

end rtl;

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

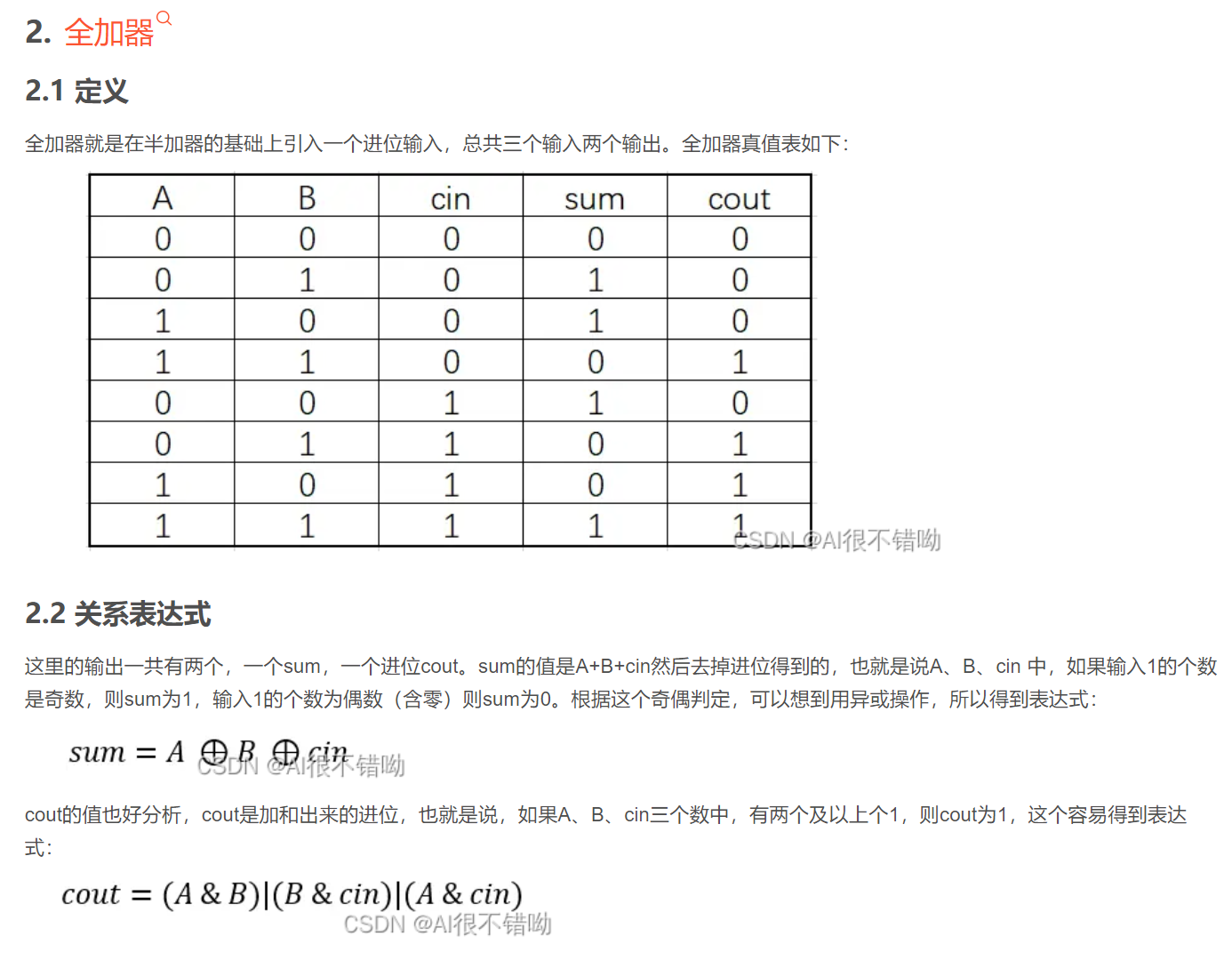

f_adder.vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity f_adder is

Port (

in0_i, in1_i, in2_i : in std_logic;

sum_o, carry_o : out std_logic

);

end f_adder;

architecture rtl of f_adder is

component h_adder

port (

in0_i, in1_i:in std_logic;

s_o, cry_o :out std_logic

);

end component;

signal s1_s, s2_s, s3_s : std_logic;

begin

h1: h_adder port map(in0_i=>in0_i,in1_i=>in1_i,s_o=>s1_s,cry_o=>s2_s);

h2: h_adder port map(in0_i=>s1_s,in1_i=>in2_i,s_o=>sum_o,cry_o=>s3_s);

carry_o <= s2_s or s3_s;

end rtl;

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

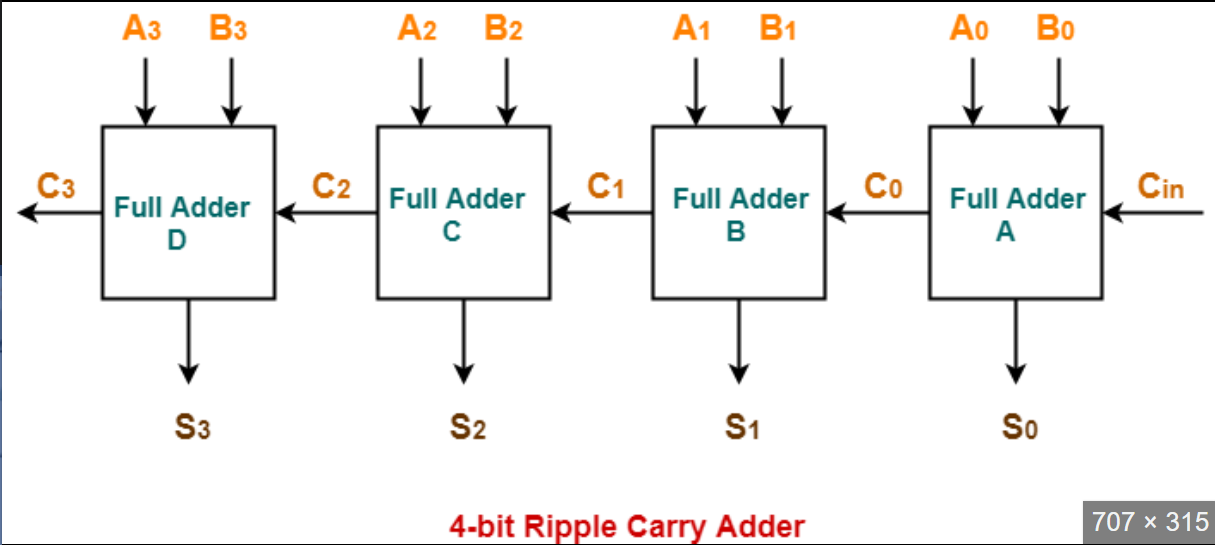

rip_cry_adder.vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity rip_cry_adder is

generic (

BUS_WIDTH : natural := 8

);

port (

cry_i : in std_logic;

in0_i, in1_i : in std_logic_vector(BUS_WIDTH-1 downto 0);

sum_o : out std_logic_vector(BUS_WIDTH-1 downto 0);

cry_o : out std_logic

);

end rip_cry_adder;

architecture rtl of rip_cry_adder is

component f_adder

port (

in0_i, in1_i, in2_i : in std_logic;

sum_o, carry_o : out std_logic

);

end component;

signal cry_s : std_logic_vector(BUS_WIDTH downto 0);

begin

cry_s(0) <= cry_i;

adder_gen:

for i in 0 to (BUS_WIDTH-1) generate

adder: f_adder port map(in0_i=>in0_i(i),in1_i=>in1_i(i),in2_i=>cry_s(i),sum_o=>sum_o(i),carry_o=>cry_s(i+1));

end generate adder_gen;

cry_o <= cry_s(BUS_WIDTH);

end rtl;

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31