Ch07 State Machine

Yang Haoran 1/1/2023 FPGAVHDL

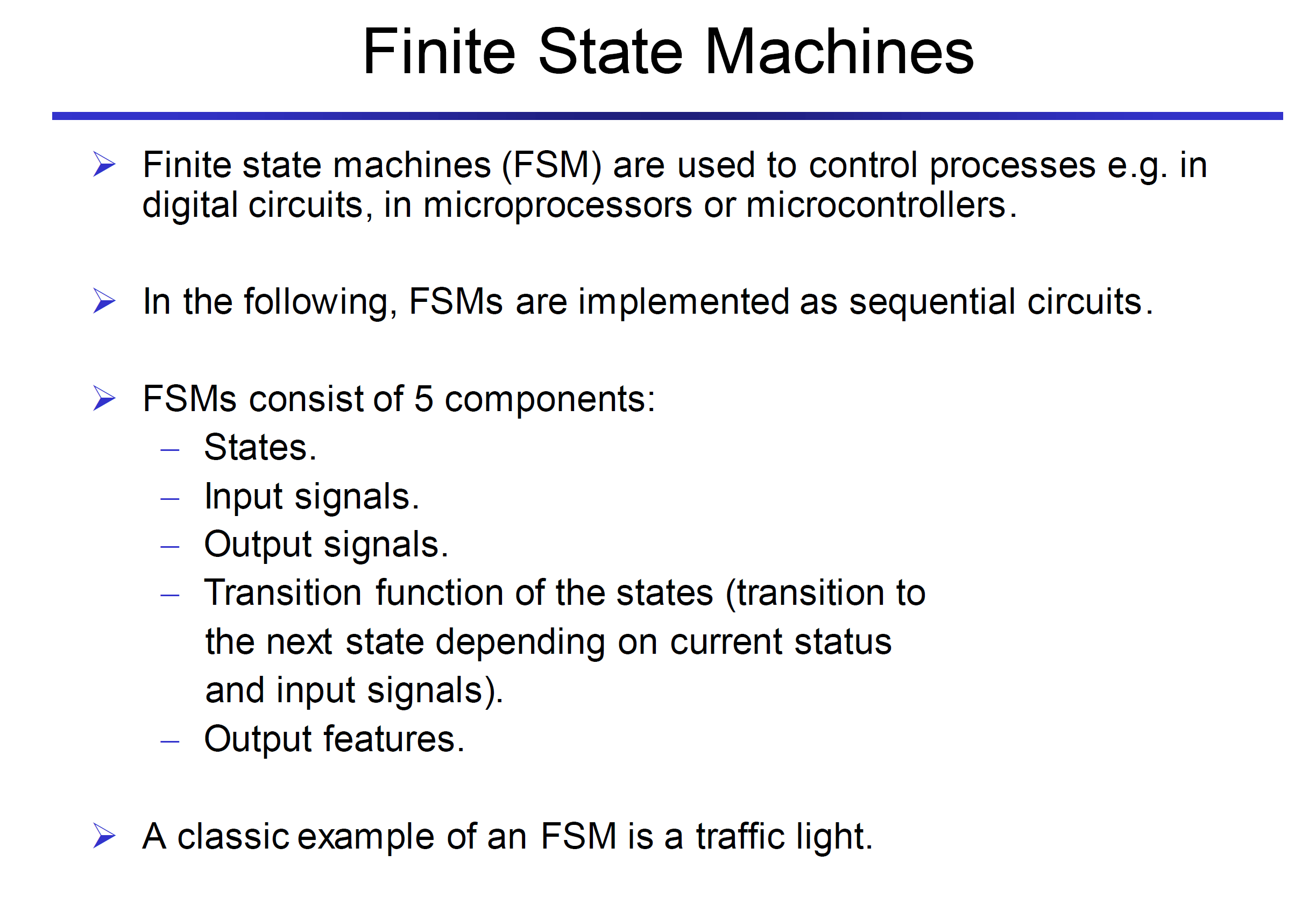

# FSM

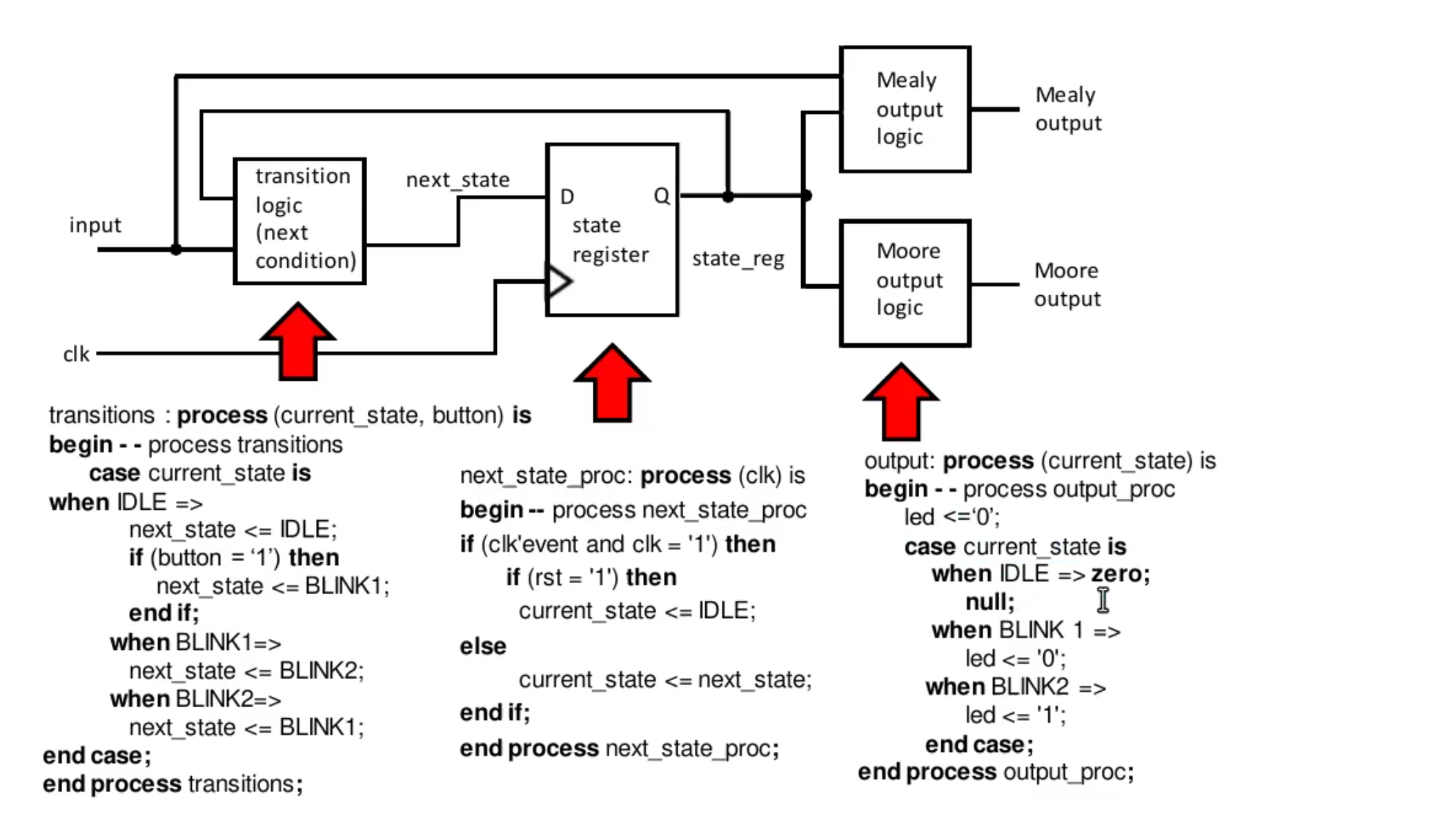

- 第一个moore,第二个mealy

- 右边是moore,因为和input无关

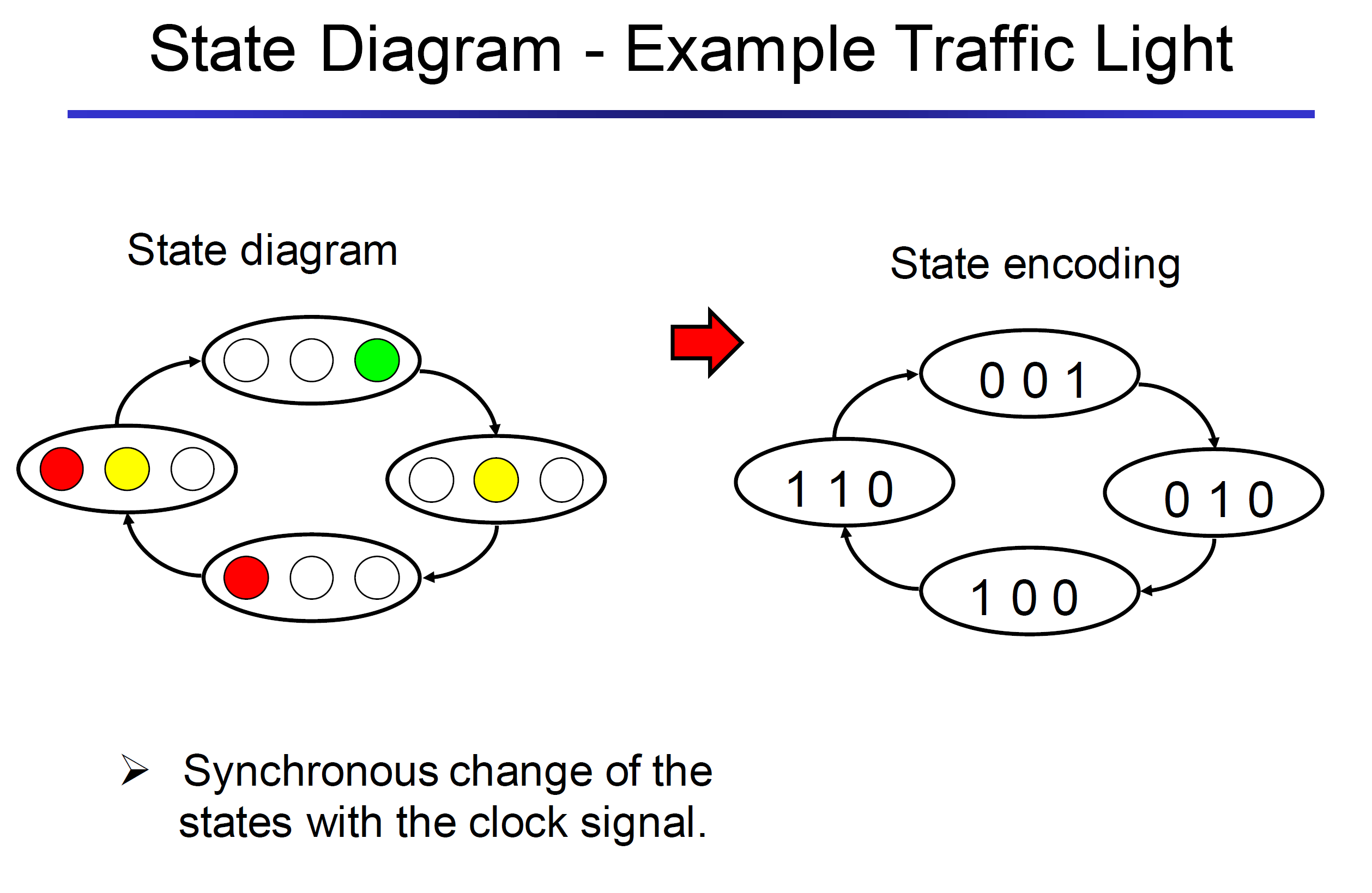

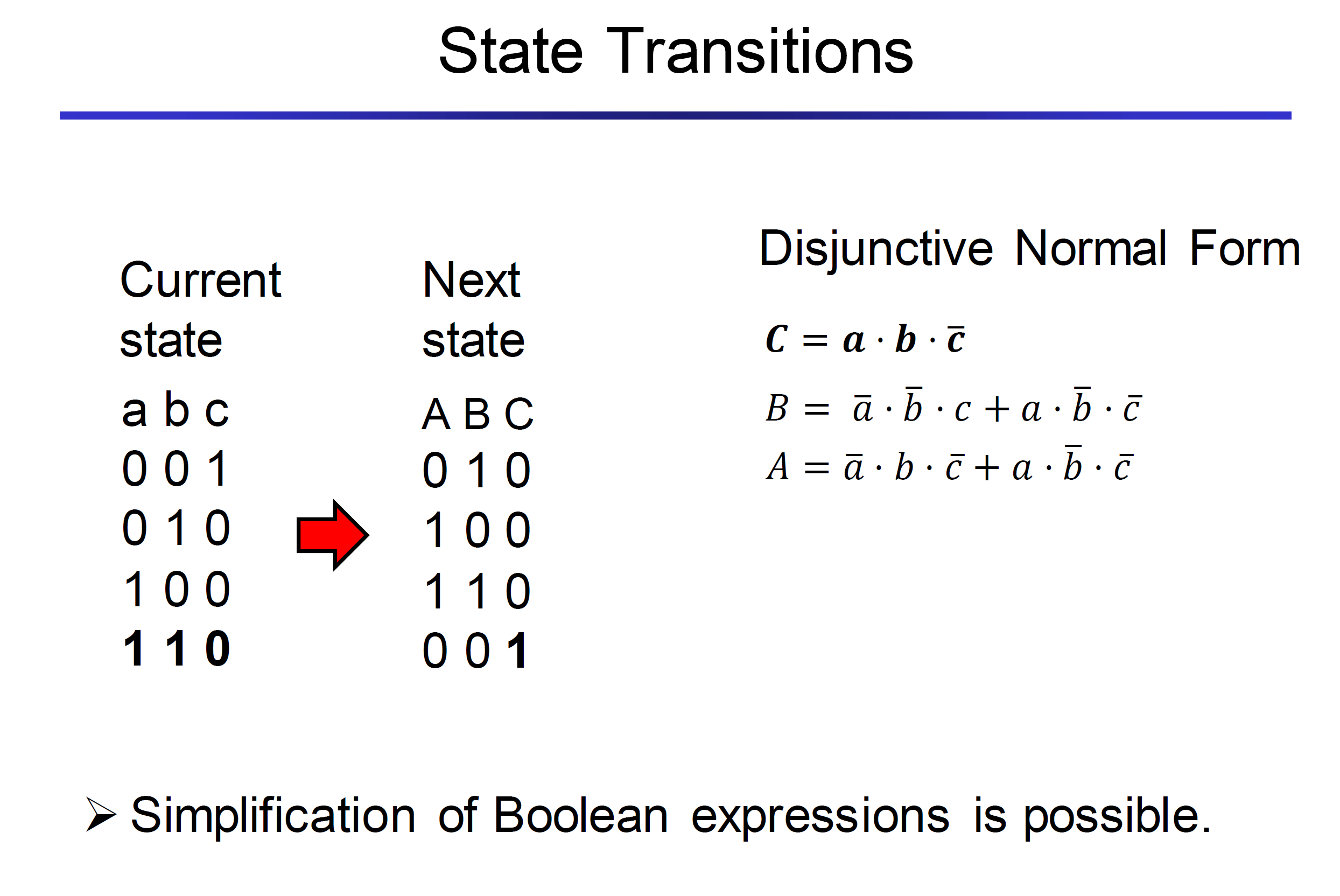

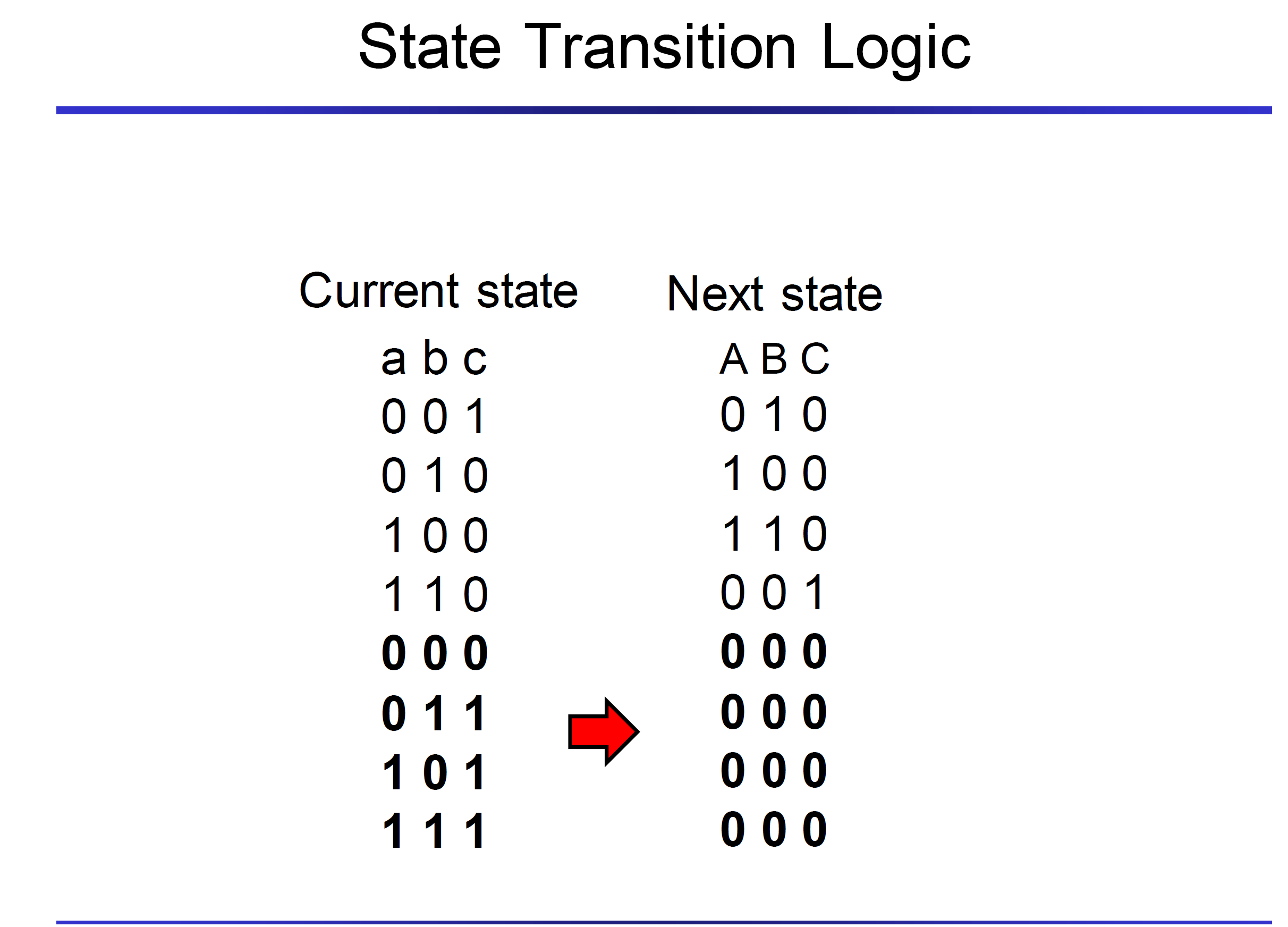

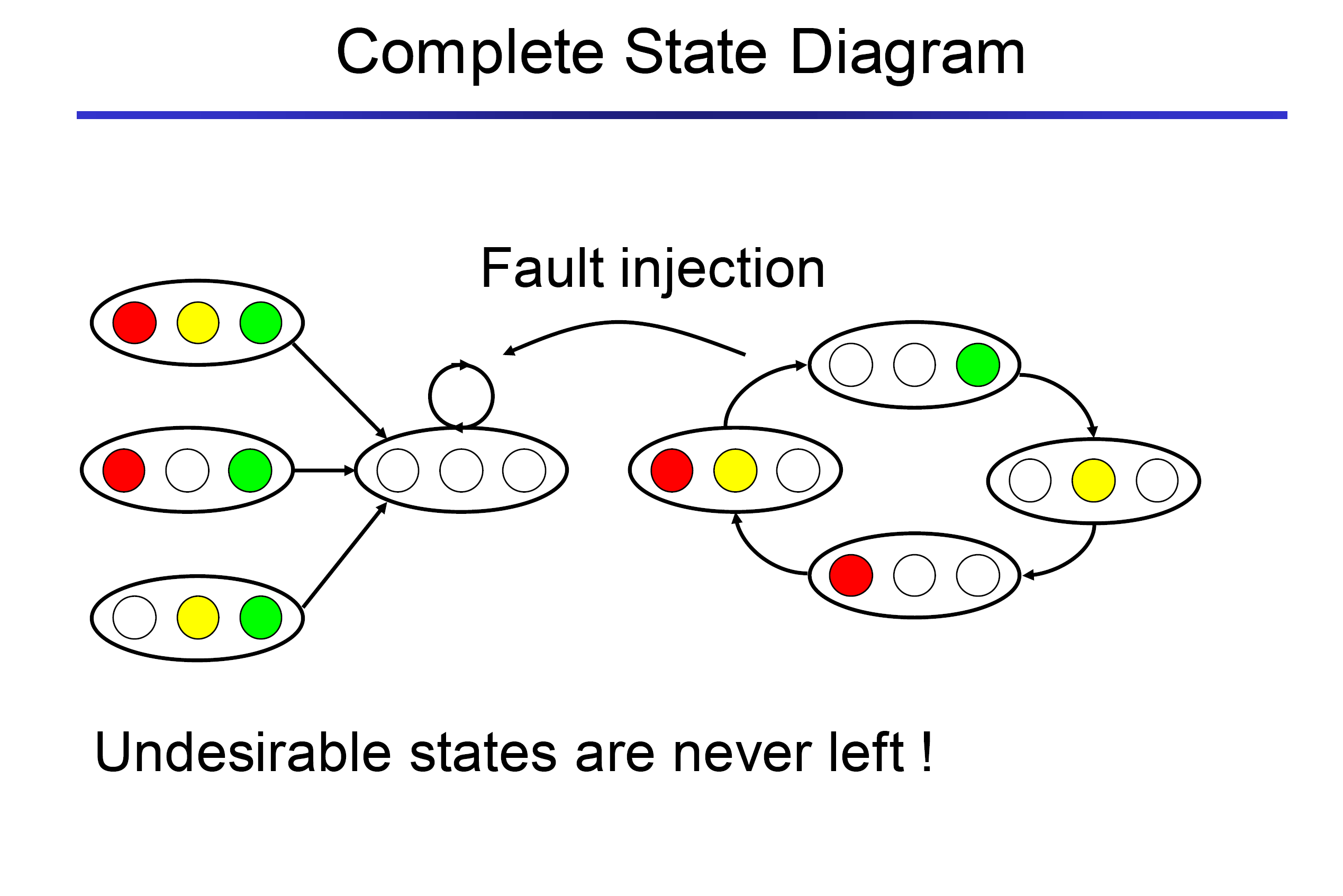

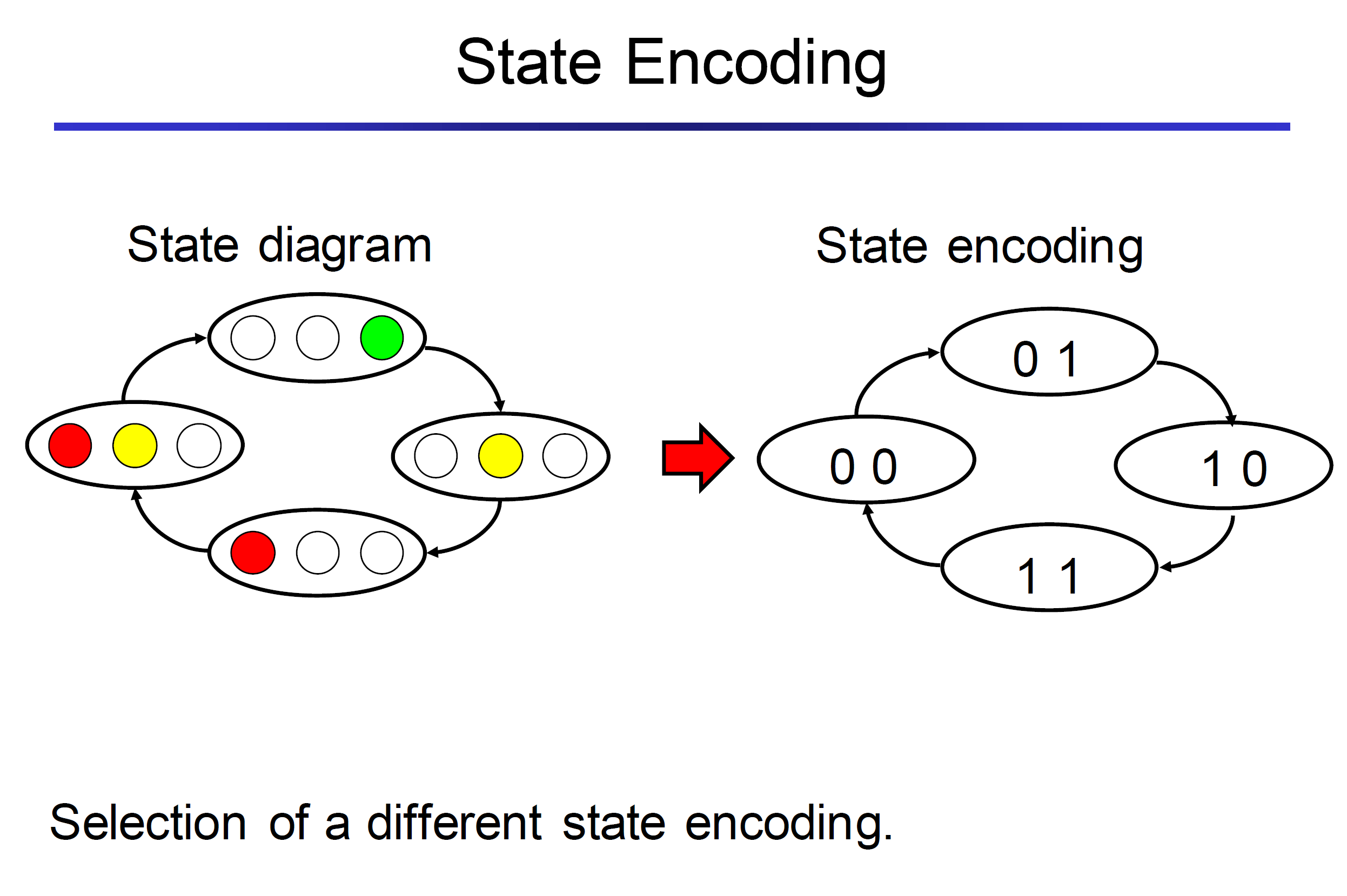

# 给状态编码的时候,可能有多余的状态,就会引起异常,比如红绿灯,而且不会返回正确的状态

- 解决方案1:把状态图画完整

- 解决方案2:重新选择状态编码

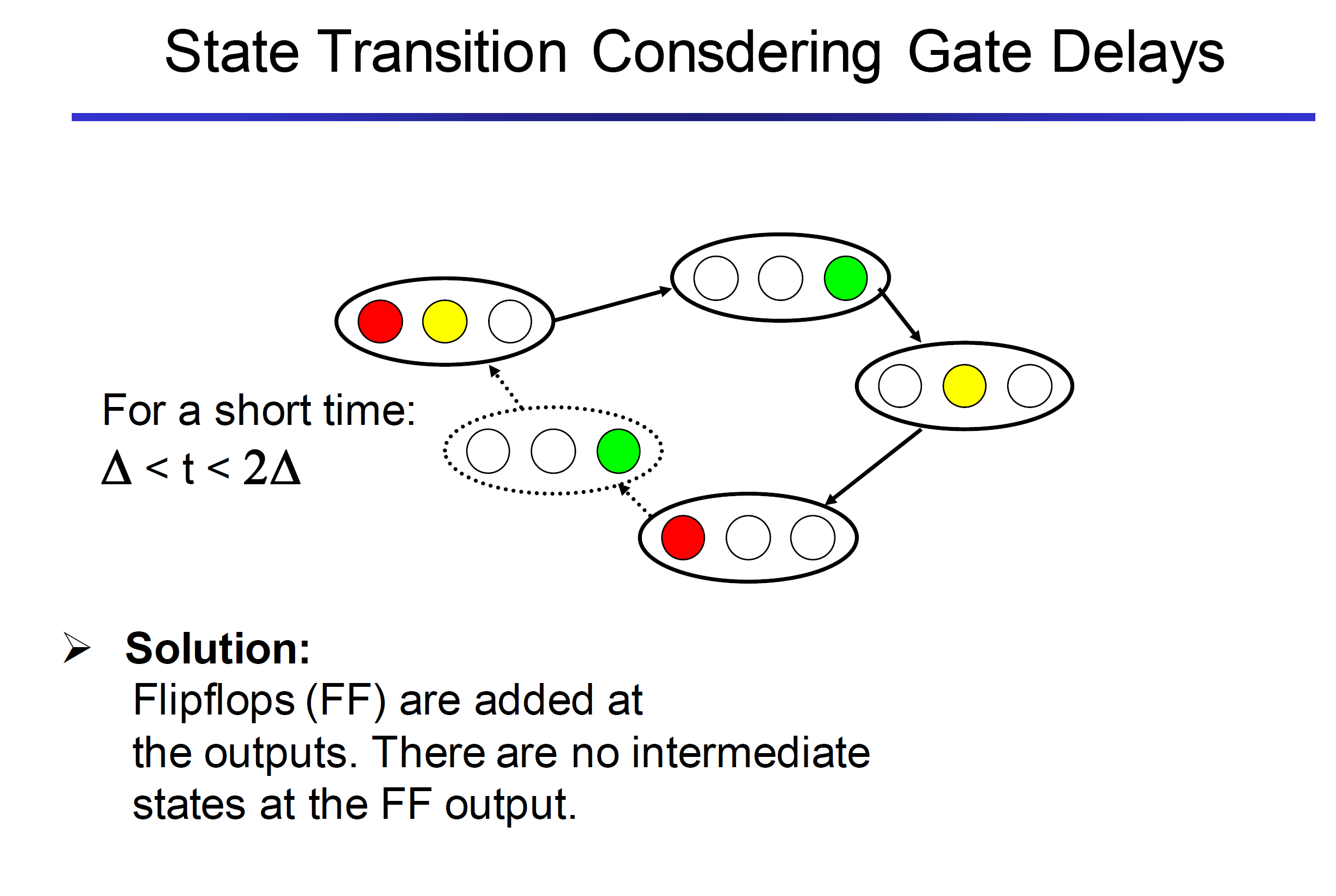

门电路会有延迟,为了避免出现不想要的状态可以在输出的地方加一个Flipflop,但是这样就会要把时钟信号设计的非常大

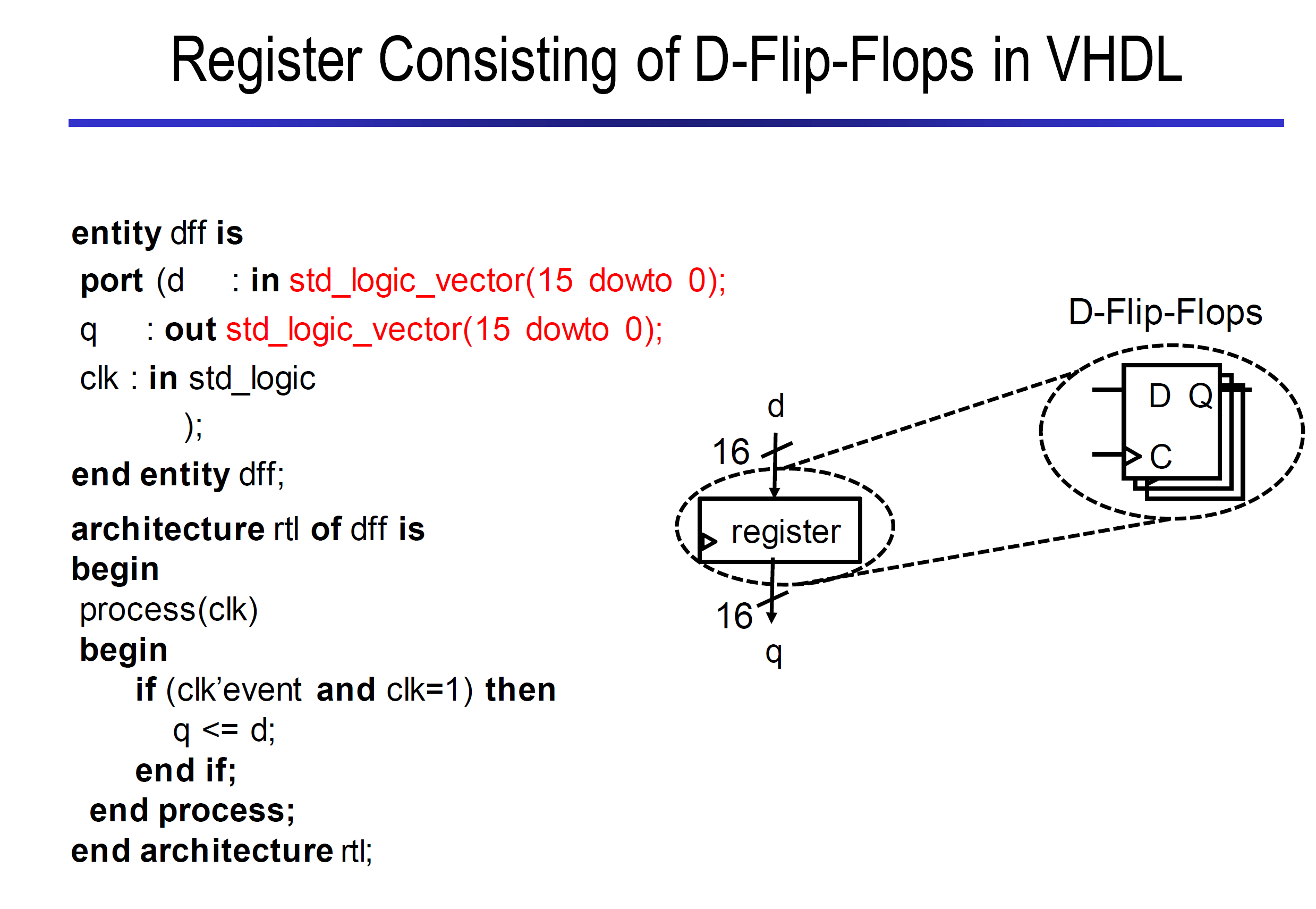

寄存器有好多D flipflop产生

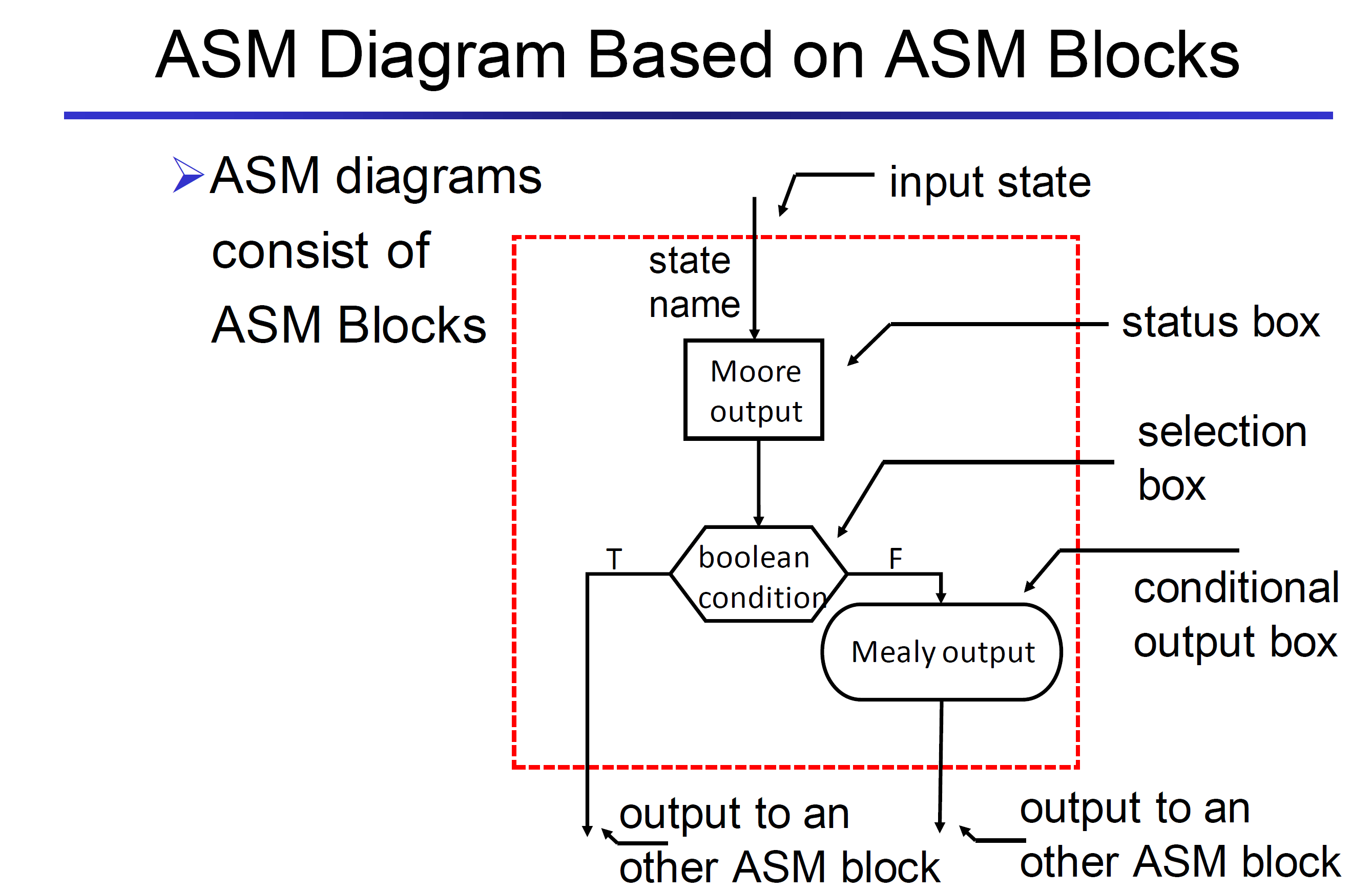

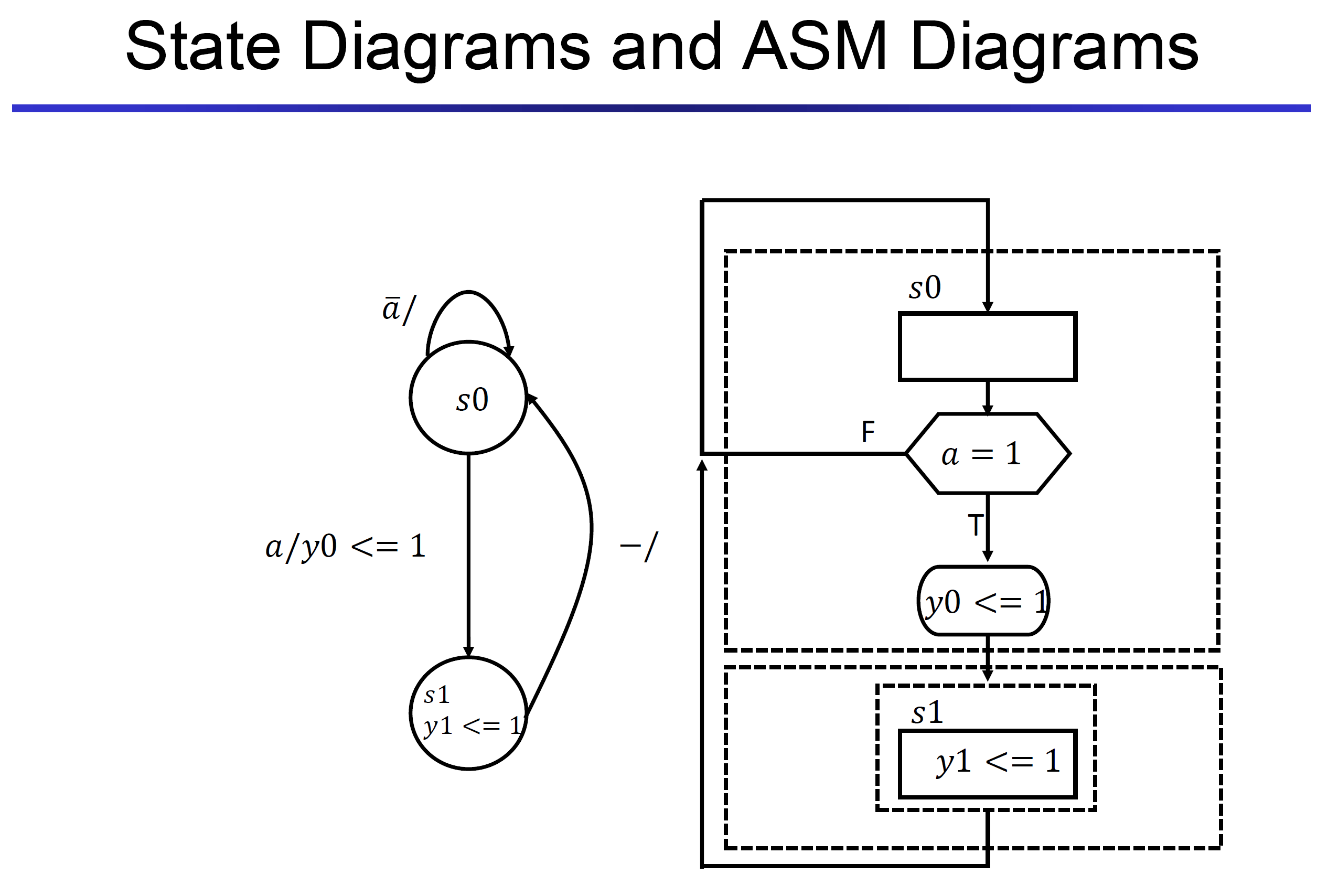

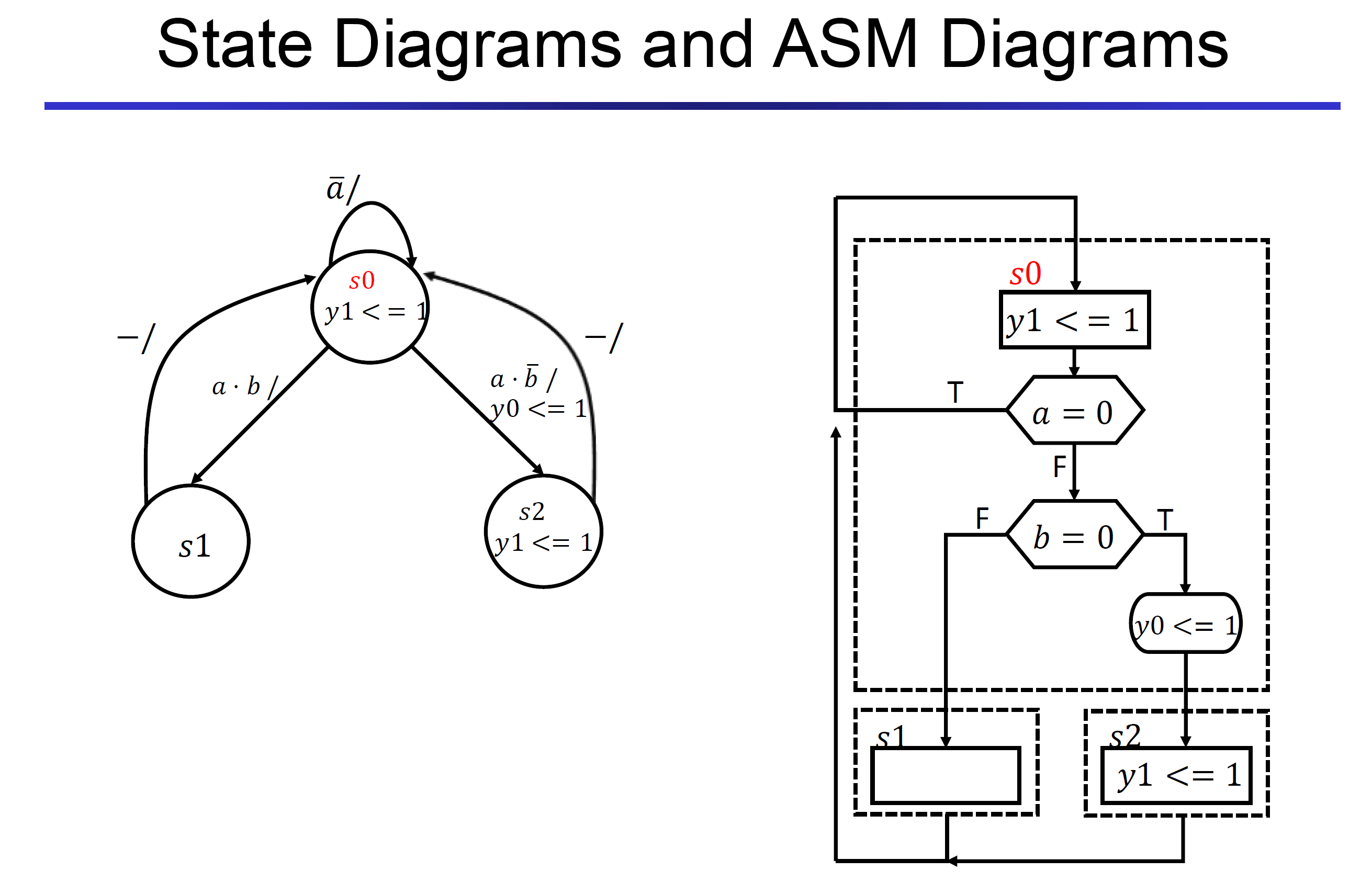

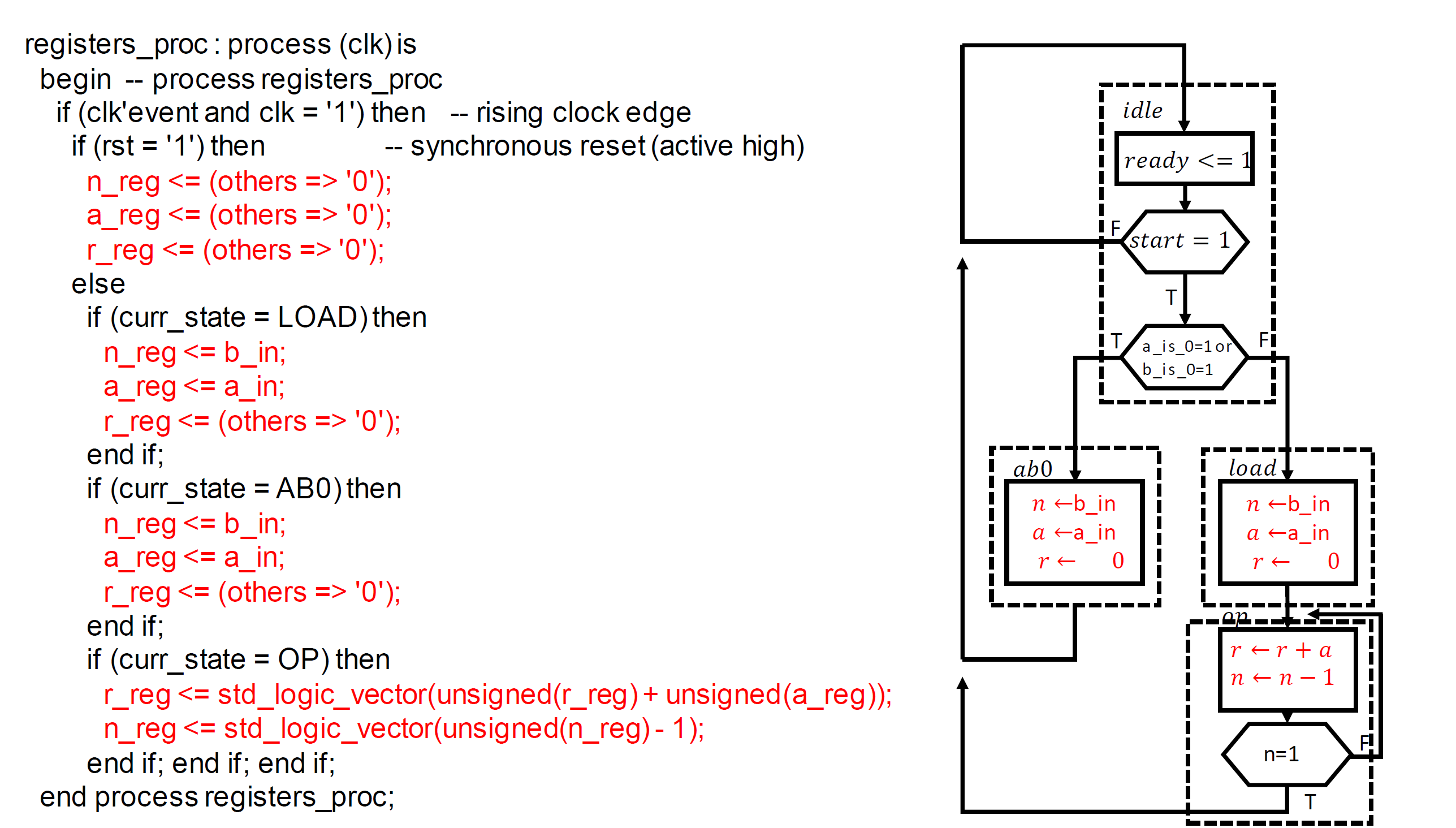

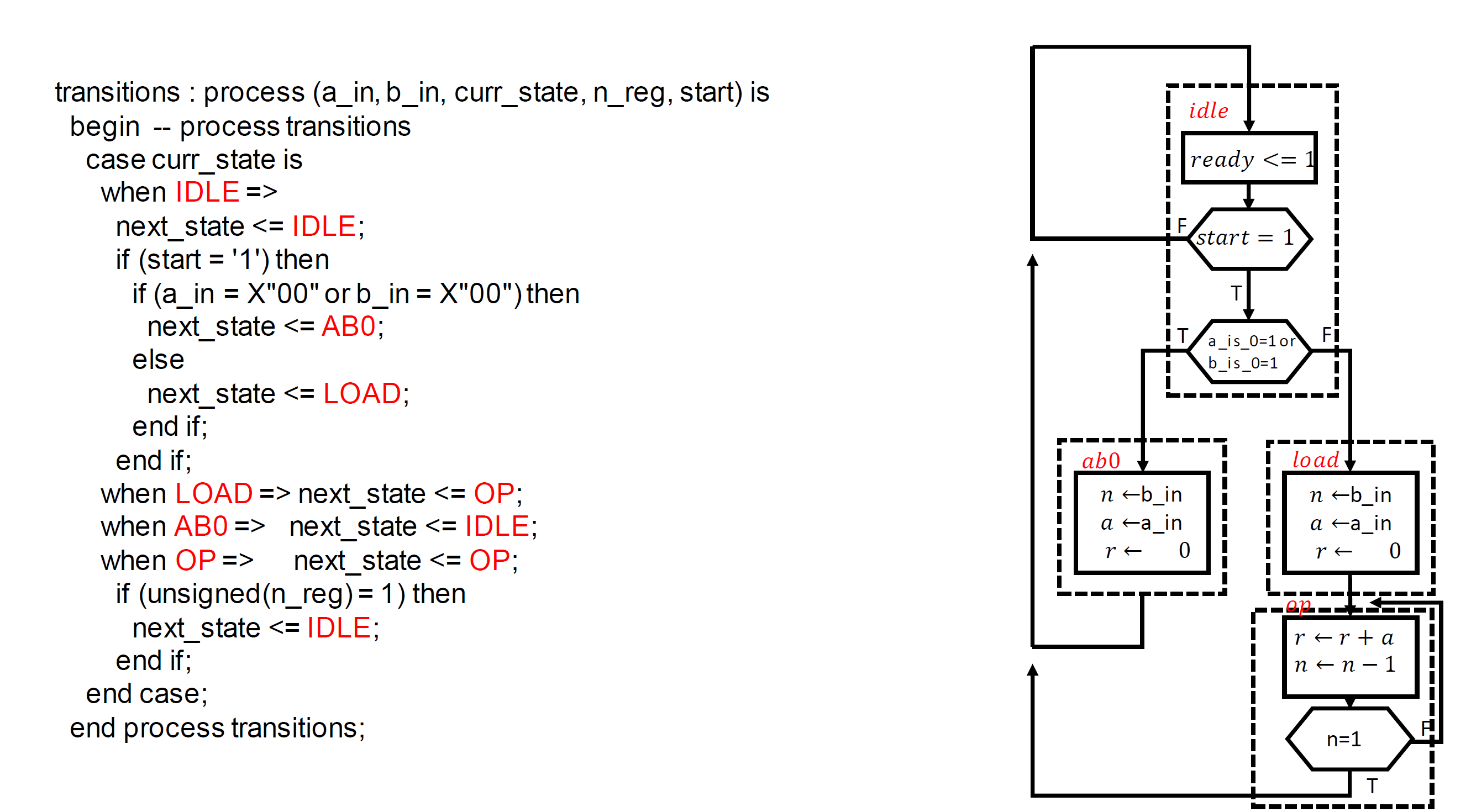

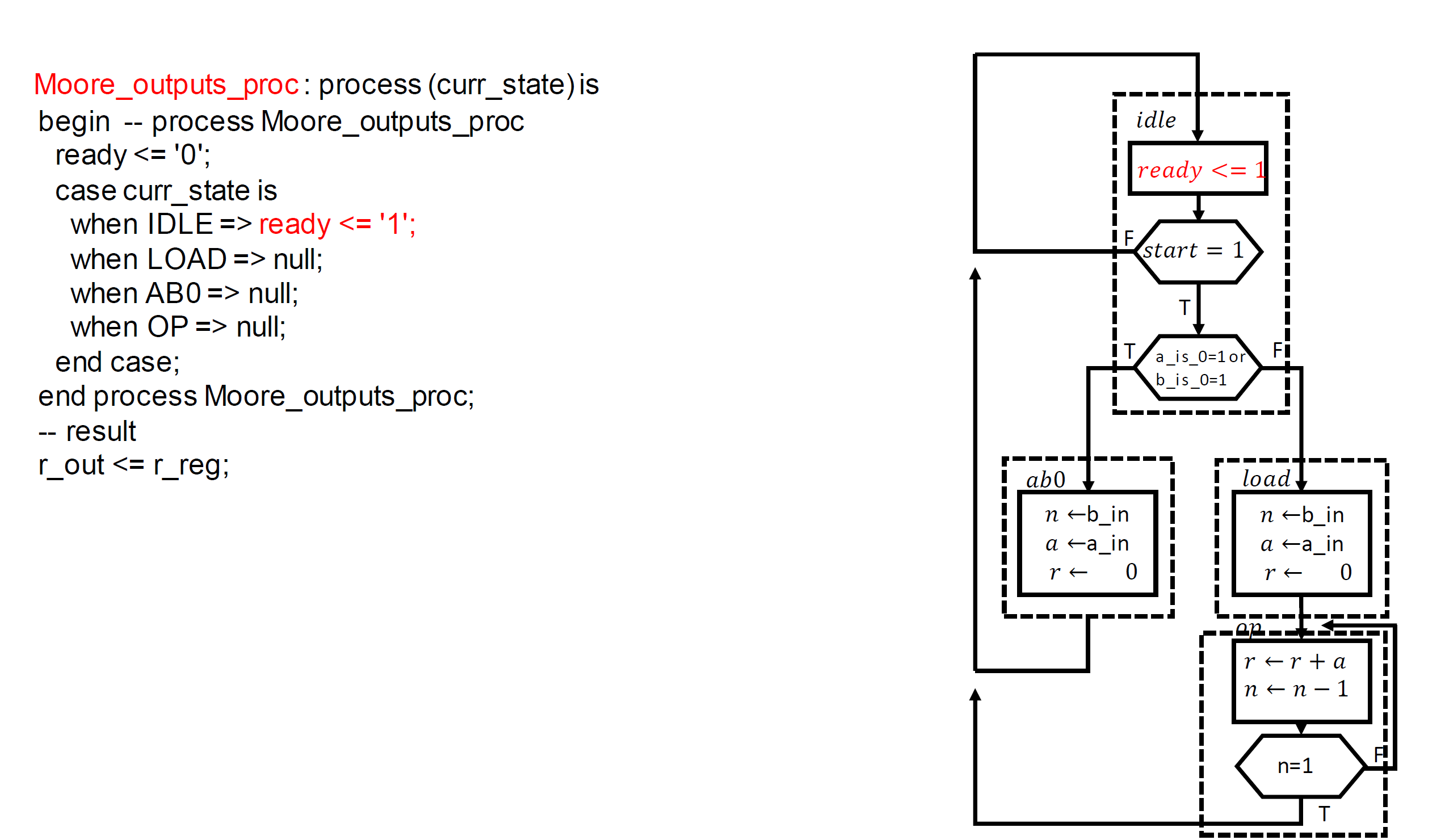

FSM可以用State diagram或者ASM来表达

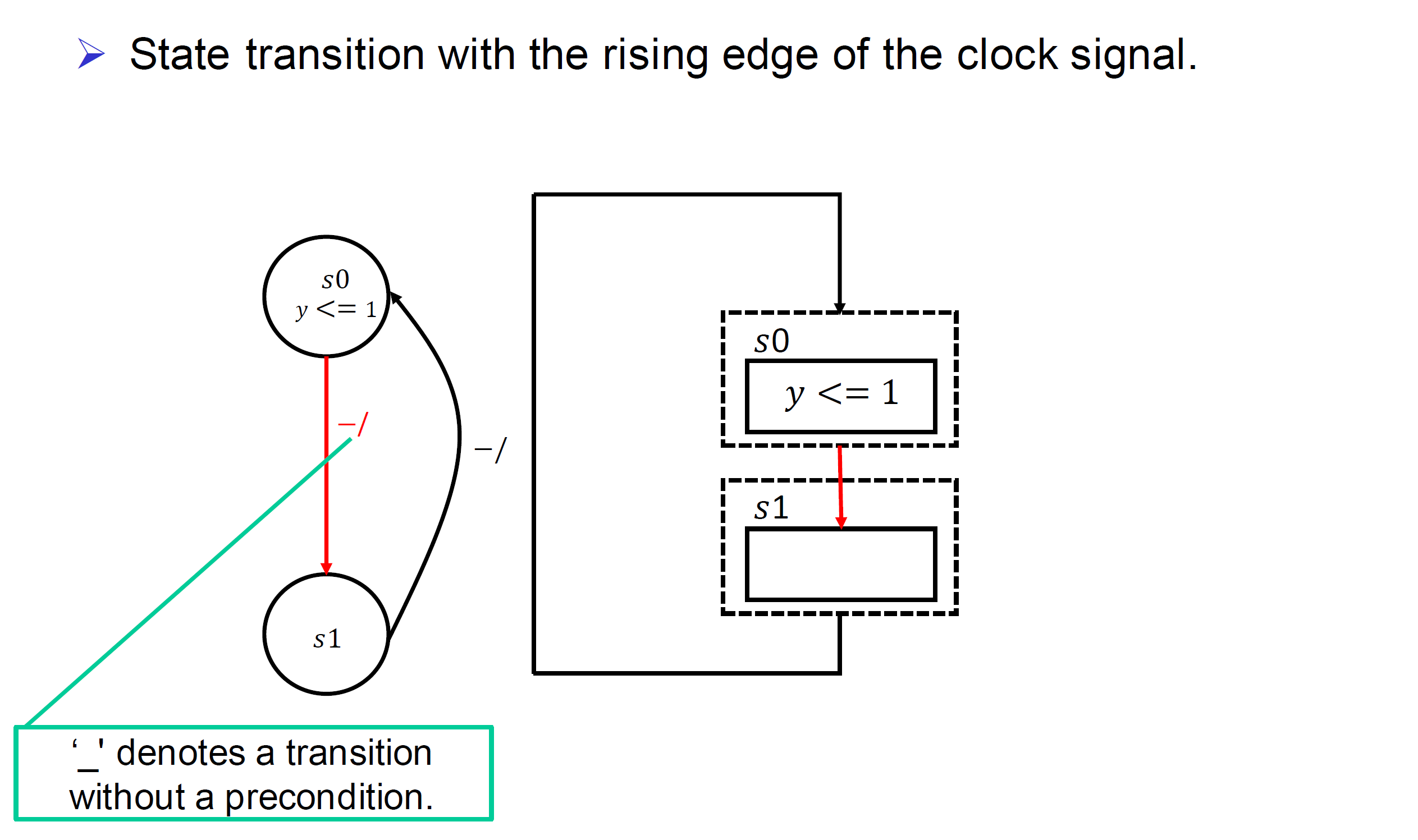

- 在state里面的是moore,在线上的是mealy

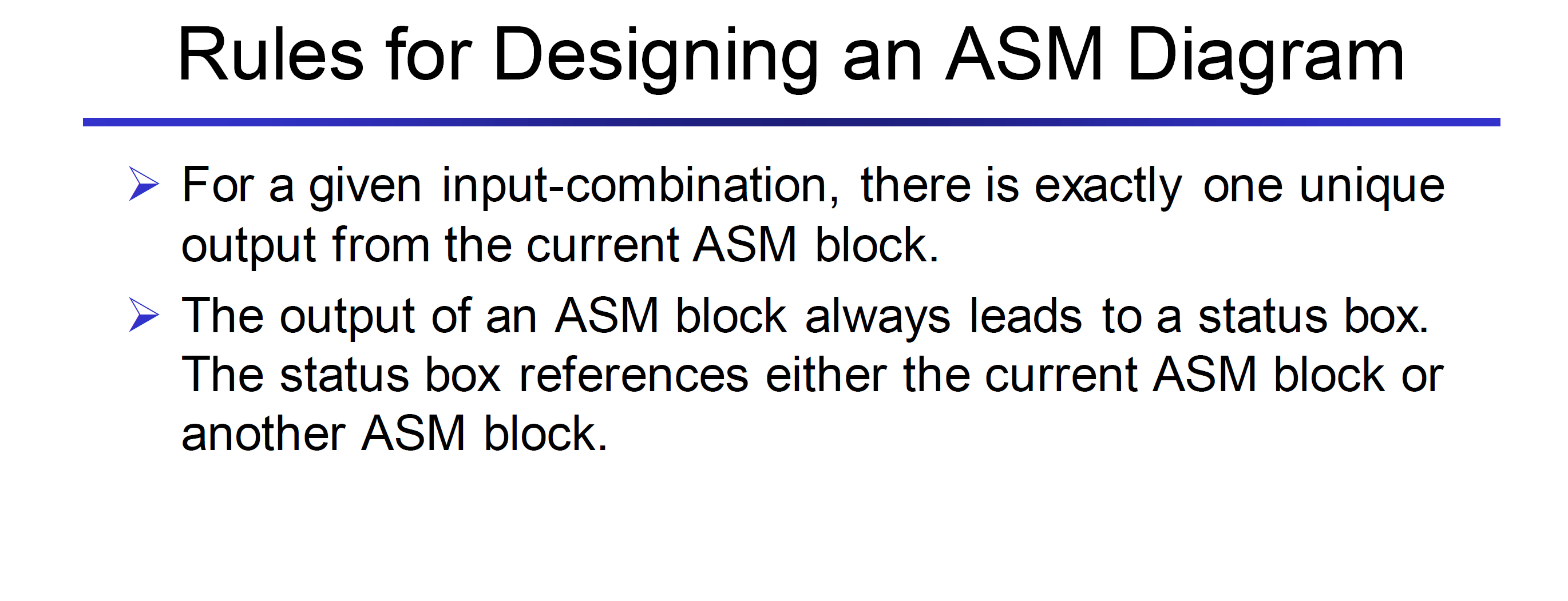

ASM

- 一个框框是一个状态

- 因为moore只和输入有关系,所以在状态改变的一开始,但是mealy会根据输入做一些判断

- 框把状态和两条输出边给框起来

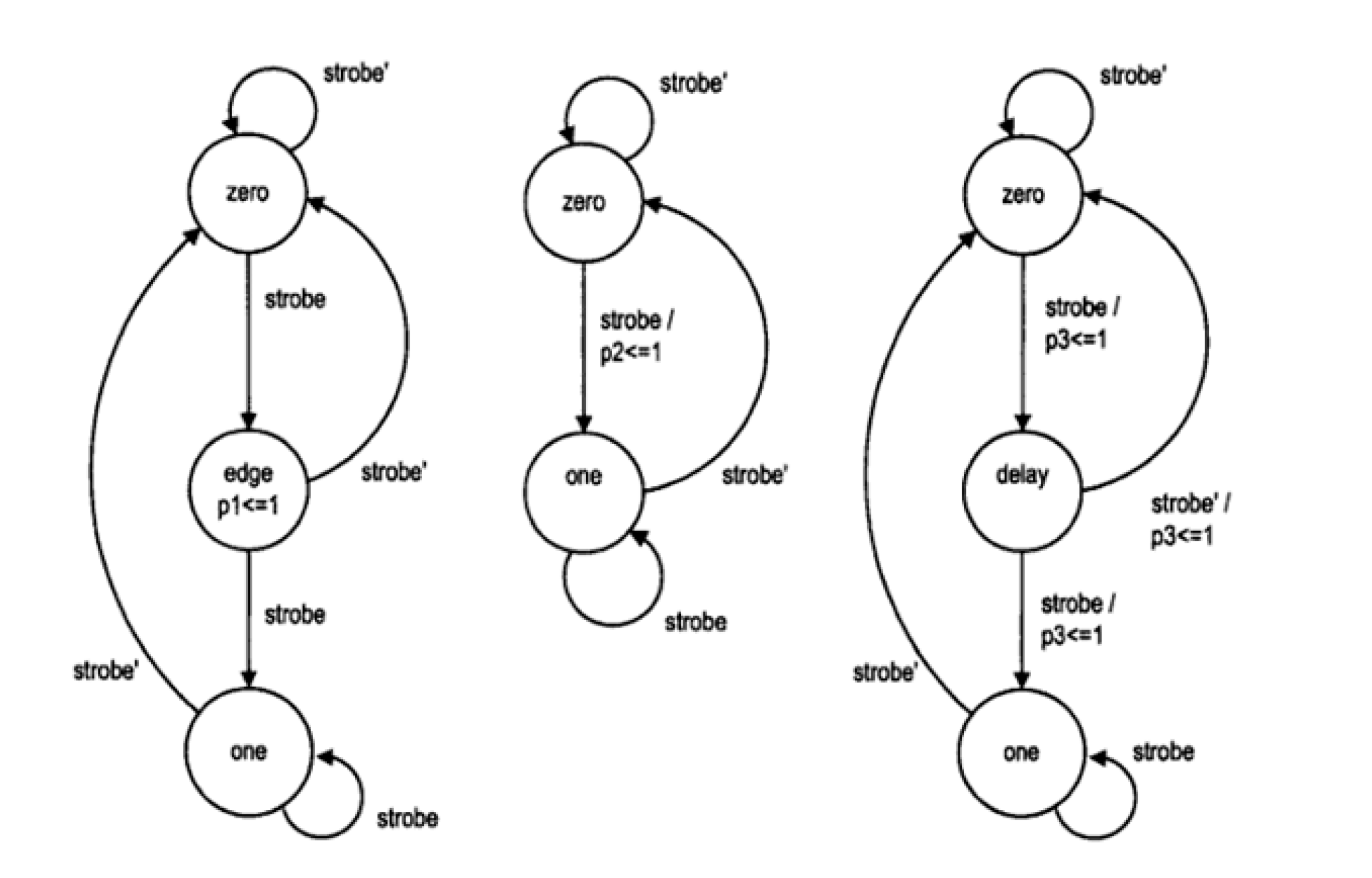

state的方框里是register:

控制状态转换是transitions

输出与状态之间是moore

- Distriburted RAM 不同步读,同步写、

- 要实现同步读可以加一个FF

- Block RAM 同步读,同步写